上海市集成电路高技能人才培养基地

集成电路设计培训课程

- 【集成电路培训展示课程】

- 1、IC系统级设计仿真招生简章

-

2、集成电路版图设计招生

简章(进阶) -

3、集成电路版图设计招生

简章 -

4、数字IC后端设计线下小

班课招生简章 -

5、数字电路布局布线设计

招生简章 -

6、现场可编程门阵列(FPGA)

及异构系统的软硬件设计

招生简章 -

7、芯片接口电路仿真测试

招生简章 -

8、芯片可测试性电路设计

仿真招生简章(DFT) -

9、运算放大器电路设计仿

真招生简章

一、培训对象

1、从事集成电路设计的工作的人员;

2、从事集成电路验证的工作的人员;

3、从事FPGA设计及Silicon测试的工作人员。

二、培训目标

1、熟练掌握目前主流的验证语言SystemVerilog在验证中的使用;

2、熟练掌握验证方法学UVM;

3、能够应用SV独立的搭建层次化的验证平台;

4、能够独立采用UVM搭建完整的模块级验证平台;

5、能够结合验证方法学、SV进行实例操作完整掌握熟悉设计规格、制定验证方案、完成验证平台搭建、开发测试用例、验证执行、覆盖率验收;

6、参考业界一流公司的验证流程,能完成相关的文档并逐一答辩通过。

三、培训特色

2注重理论和实践的结合,着重实训技能,结合完备的基础理论培训,参照一线公司的验证流程来指导实训为特色

2验证方案的制订:包含设计规格的整理和肢解,验证方法和平台的选择,包括激励的产生、参考模型的设计、随机策略、自比对策略、覆盖率保证和验证复杂度以及开发进度的保障等等。需要验证人员准备相关的文档进行答辩,来培养独立承担复杂模块验证的能力。

2验证覆盖率的收敛:包含产品规格和测试用例的全覆盖,还包括功能覆盖率,代码覆盖率,让学员按照严格的流程来通过验证验收。

四、 培训费用

1、培训费2500元。包含教材费、场地费、线上平台、实训账号等。

五、培训计划

1、线下培训总课时:80个课时(线下课程为主,线上课程为辅),持续2-3个月(课时按实际课程进度进行调整)

2、培训时间:每周末一天(国家法定假日另行安排)

3、培训地点:上海硅知识产权交易中心(宜山路333号汇鑫国际大厦1号楼1706室)

4、开班形式:小班授课,保证每人1台PC;全流程开通vnc登录账号,任何时间随时登录进行工具学习和实战操作,授课老师提供技术支持与答疑

5、开班时间:招满即开

六、培训师资

本项目培训师资人员均是具有10年以上专精于集成电路验证的资深专家,拥有对复杂Soc的验证经验、项目管理与带队经验。

vJimmy Peng:具有十年验证相关工作经验,项目规模在千万门以上,工艺14/16nm/20nm。产品涉及手机,无线通信及多媒体终端的核心芯片。涉及到的IP包括:WCDMA、GSM、TD、Wifi、USB2、USB3、MIPI、 CSI/DSI、CE、SD、SDIO、PCIE、EMMC、音视频核心算法IP;以及在SOC level的低功耗和POWER仿真。

vWill Zhang:具有十年左右的验证工作经验,精通各种主流验证技术和方法学,带领团队进行ip级和soc级的验证工作,同时负责验证流程的维护和开发。

vMichael He:项目规模在千万门以上,工艺40/28nm。产品涵盖基站基带芯片和Wi-Fi移动芯片等。涉及到的集体包括:multi-layer bus matix,多核ARM CPU,ddr3等,以及低功耗验证。

七、课程大纲

(一)SystemVerilog语言基础

1、理论教学内容

(1)学习和掌握数据类型

1)内嵌的基本数据类型

2)大小固定的数组

3)动态数组(Dynamic Arrays)

4)能够正确理解和掌握队列(Queue)

5)枚举类型

6)字符的使用

7)常数

8)创建新的类型和数据结构

(2)过程语句和程式

1)Procedure Statements 介绍

2)理解和掌握任务

3)理解和掌握函数

4)时间的定义和使用

5)程式的参数传递

6)SystemVerilog的接口介绍

(3)技能实训内容

(4)SV基本数据类型的定义、赋值、循环打印

(5)数组的声明、赋值、打印,包括单维、多维数组

(6)简单加法器的Task实现、并写简单的TB来调试task

(7)函数的实现,与调试

(8)调试Task,函数的参数传递

(9)为Router搭建简单的TB并用interface实现对DUT的封装

(二)SystemVerilog TB的架构

1、基础理论教学

(1)层次化验证环境的概念介绍

(2)TB对DUT的封装

(3)Interface的构建

(4)Interface的驱动和采样

(5)数据结构的定义

(6)随机数与数据生成的管理

(7)激励的生成初步介绍

(8)激励的时序管理

(9)TB顶层的基本功能

(10)有四个接口的ATM Router实例

2、技能实训内容

(1)有四个接口的ATM Router 实例的调试

1)开发TB对DUT进行封装

2)定义数据接口

3)实现接口、生成激励

4)管理TB的时序

(三)UVM 验证方法学

1、理论教学内容

(1)UVM验证方法学的介绍

(2)UVM验证环境各个部件的要点

(3)UVM Driver要点

(4)UVM Sequencer要点

(5)UVM Monitor要点

(6)UVM Vif 要点

(7)UVM phase 要点

(8)UVM TLM 接口要点

(9)UVM RAL要点

(10)UVM 环境的集成

(11)Router的典型UVM验证环境应用实例分析

2、技能实训内容

(1)为Router开发完整的UVM验证环境

1)实战开发所有的UVM部件Driver、Monitor、Sequencer

2)定义TLM 接口、Vif

3)完成环境的集成

4)调试

(四)UVM验证环境实训

1、理论教学内容

(1)验证环境的架构设

(2)UVM Transaction的定义和实现

(3)TLM 通信,put、get、analysis port

(4)能够掌握UVM Driver的实现方法

(5)能够掌握UVM Sequencer的实现方法

(6)能够掌握UVM Monitor的实现方法

(7)能够掌握UVM Agents的实现方法

(8)通用Router设计要点

(9)通用I2C设计要点

2、技能实训内容

(1)为Router开发完整的UVM验证环境

1)实战开发所有的UVM部件Driver、Monitor、Sequencer

2)定义TLM 接口、Vif

3)完成环境的集成

4)调试

八、联系方式

联系人:Gina Hong/021-61154610-8801 张勇021-61154610-8850

邮箱:gina.hong@ssipex.com yong.zhang@ssipex.com

微信:

一、培训对象

1、集成电路版图设计零基础的理工科毕业生(包括微电子,物理系,材料系,计算机等相关专业)。

二、培训目标

中级工程师(进阶班):在初级工程师基础上,通过进阶深入培训,让学员完成经典版图的实战训练,达到产品级别的版图设计能力。

三、培训特色

1、上海硅知识产权交易中心拥有全国优秀的版图学习平台和硬件支持,包括最先进的设计工具,验证工具。

2、为保证培训质量,学习课程和实训以线下为主,作业,答疑和课外学习以线上辅助。

四、培训计划

1、线下培训总课时:80 个课时(线下课程为主,线上课程为辅)工作日可随时提供线上辅导(时间不计入),课程时间 2-3 个月(按实际课程进度进行调整)

2、培训时间:每周末一天(国家法定假日另行安排)

3、培训地点:上海硅知识产权交易中心(宜山路 333 号汇鑫国际大厦 1 号楼 1706 室)

4、开班形式:小班授课(20 人以下),保证每人 1 台 PC;全流程开通 vnc 登录账号,任何时间随时登录进行工具学习和实战操作,授课老师提供技术支持与答疑

5、开班时间:招满即开

五、 培训费用

进阶班培训总费用:3000元,与学员签署协议约定

六、培训师资

培训讲师是具有十多年以上专精亍集成电路版图实践的资深专家,在工艺和器件、版图设计规则,物理验证,版图工具等领域有着丰富的理论和实践经验。

William kin: 拥有近 17 年集成电路版图设计经验,拥有全流程的版图设计技术,有在Qualcomm 等顶尖企业长期任职项目主管经验,目前为一家新兴芯片设计公司版图组资深经理,组建了公司 20 人的版图团队,领导了公司近 10 款超大规模芯片的版图工作幵全部成功量产。

七、课程大纲

1、版图基础知识基础操作考核(详细辅导达到考核标准)2天

2、OPAMP的版图设计及验证(达到产品级别)1天

3、Bandgap的版图设计及验证(达到产品级别)2天

4、包含inv/nand2/dff2/OPamp/Bandgap/ESD/PADIO等模块的中等规模芯片TOP 级完整芯片版图的设计及验证3天

5、芯片Tapeout的流程。1天

6、模拟面试就业指导。1天

八、联系方式

联系人:Gina Hong/021-61154610-8801 张勇021-61154610-8850

邮箱:gina.hong@ssipex.com yong.zhang@ssipex.com

微信:

一、培训对象

1、集成电路版图设计零基础的理工科毕业生(包括微电子,物理系,材料系,计算机等相关专业)。

2、相关专业有意愿从事集成电路版图设计的人员。

二、培训目标

初级工程师:通过培训使零基础学员全面掌握集成电路版图设计知识点和技能,成为一个合格的初级工程师,能承担普通的IC版图设计工作。

三、培训特色

1、上海硅知识产权交易中心拥有全国优秀的版图学习平台和硬件支持,包括最先进的设计工具,验证工具。

2、为保证培训质量,学习课程和实训以线下为主,作业,答疑和课外学习以线上辅助。

四、培训计划

1、线下培训总课时:80个课时(线下课程为主,线上课程为辅),持续2-3个月(课时按实际课程进度进行调整)

2、培训时间:每周末一天(国家法定假日另行安排)

3、培训地点:上海硅知识产权交易中心(宜山路333号汇鑫国际大厦1号楼1706室)

4、开班形式:小班授课(40人以下),保证每人1台PC;全流程开通vnc登录账号,任何时间随时登录进行工具学习和实战操作,授课老师提供技术支持与答疑

5、开班时间:招满即开

五、 培训费用

初级班培训总费用:2500元

六、培训师资

培训讲师是具有十多年以上专精于集成电路版图实践的资深专家,在工艺和器件、版图设计规则,物理验证,版图工具等领域有着丰富的理论和实践经验。

William kin: 拥有近17年集成电路版图设计经验,拥有全流程的版图设计技术,有在Qualcomm等顶尖企业长期任职项目主管经验,目前为一家新兴芯片设计公司版图组资深经理,组建了公司20人的版图团队,领导了公司近10款超大规模芯片的版图工作并全部成功量产。

七、课程大纲

(一)集成电路版图设计基础课程

1、集成电路的概念和发展前景

2、集成电路制造工艺流程

3、集成电路和集成电路版图设计

4、集成电路版图设计流程

(二)版图设计环境

1、Linux操作系统

2、Linux指令精简版

3、vi指令操作

4、认识PDK

5、工艺文件,规则解读

6、工作环境设置

7、virtuoso版图工具详解

8、layoutXL工具

9、dispay和bindkey文件

10、Calibre验证工具详解

11、图操作快捷键

(三)集成电路设计中的器件和单元

1、有源和无源器件:MOS管,diode,bipolar,电阻,电容,电感等

2、互连 contact,via

(四)MOS管及标准数字逻辑基本概念和版图实现

1、CMOS基本概念和图文认识

2、CMOS版图详解

3、CMOS版图的常用技巧

4、标准数字单元版图设计及验证(inv/nand2/nor2/nand3/nor3/OSC)

(五)版图设计规范

1、版图Match 概念和器件匹配

2、ESD版图设计

3、Latch-up效应

4、寄生效应

5、Antenna天线效应

6、保护环guardring

7: 隔离 Shielding

8、可靠性规则

9、金属密度规则

10、电迁移效应

11、封装Packaging

12、网表知识netlist

(六)模拟版图设计就业实战

1、差分放大器的版图设计实战

2、COMP版图设计实战

3、VCO版图设计

3、RF的版图设计

4、功率管的版图设计

5、PLL的版图设计

6、bandgap版图设计

7、Serdes高速版图设计

(七)TOP layout

1、Fullchip

2、floorplan

3、芯片设计流程

4、就业指导

八、联系方式

联系人:Gina Hong/021-61154610-8801 张勇021-61154610-8850

邮箱:gina.hong@ssipex.com yong.zhang@ssipex.com

微信:

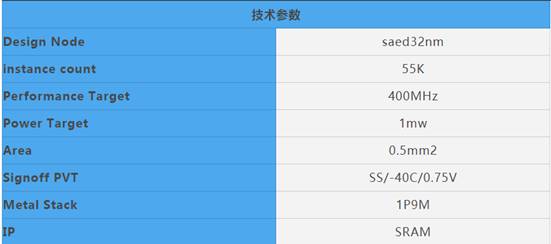

一、课程概述

后端物理设计,在整个复杂的集成电路设计生产流程中,是连接集成电路前端逻辑设计和生产制造的重要步骤,是芯片的一个重要环节,尤其是先进工艺,电路规模越大的情况下,后端物理设计和实现,显得尤其重要,因此各大公司都加以对后端实现的人力和资源投入。

二、培训对象

1、微电子及电子相关专业,想从事集成电路后端设计工作,励志进入世界一线芯片公司的学生

2、初级后端设计工程师

3、想转行从事集成电路后端设计工作的工程师

三、培训目标

1、掌握芯片设计后端流程的知识点

2、掌握芯片设计后端流程所需要的EDA工具

3、掌握实战项目的后端全流程实现

4、掌握解决后端实现中遇到的问题,掌握方法和思路

5、成为一名有实力的后端工程师

四、培训特色

1、30天集训时间,讲练结合,实时答疑

2、2位资深后端工程师倾力奉献,饱含丰富的经验总结

3、5大领域内容,覆盖:芯片设计编程、后端物理设计、静态时序分析、功耗与电源分析、物理规则验证。

五、 培训费用

数字后端线下培训班,收费2500元,10人以上(包含10人)开班,其中包含60课时线上理论录播,三天线下实训指导,理论录播观看期限为三个月,线下实训账号使用期限为一个月,具体根据课程安排。网站问答及微信群答疑服务期限从线上课程上线开始,到线下课程结束后一周。

六、课程信息

开课时间

11月23日理论课程上线

2019年12月1日:线下第一天集训实战(上海)

2019年12月8日:线下第二天集训实战(上海)

2019年12月15日:线下第三天集训实战(上海)

实训课地址:宜山路333号1705室,实训课程需自行携带笔记本电脑

七、培训师资

本项目培训师资人员均是具有10年以上专精于集成电路后端布局布线的资深技术人员,拥有对 复杂 IC 后端设计经验、项目管理与带队经验。

v 艾思:曾就职于国际TOP5芯片设计中心,担任资深主任设计工程师,10多年后端设计实现经验,独立领导后端项目,拥有数十次成功六片的经验,工艺涵盖 40/28/12/7nm 等。尤其擅长top- layout,STA,LV等后端实现关键技术领域。

v Peter:后端设计和低功耗技术专家,从事多年芯片综合、时序分析收敛和后端设计 工作,具有丰富的ASIC项目后端经验,精通静态时序分析(STA)和时序约束(SDC)相关知识。拥有7/16/28nm等多个项目流片经验,精通芯片后端实现流程、功耗分析与各种低功耗设计方案。

Bobin:9年后端设计工作经验,拥有14/28/40nm等多个项目流片经验,精通芯片后端实现流 程、逻辑综合、物理综合、时序修复。v

郭亚鹏:在Nvidia等跨国公司和国内初创公司从业12年,对从RTL到芯片量产有丰富的经验。

八、课程大纲

(一)、芯片后端设计编程基础

1)Unix环境与cshell编程

2) 时序库的定义

3)TCL编程基础

(二)、芯片后端设计

编程基础芯片后端物理设计 (ICCompiler)

1)数字后端设计流程概览

2)ICC工具初接触

3)ICC 数据输入

4)版图规划 (Floorplan)

5)电源规划 (power planning)

6)自动布局 (Placement)

7)时钟树综合 (Clock Tree Synthesis)

8)时钟后优化(post_cts_opt)

9)绕线 (Route)

10)芯片完成(chip-finish)

11)ECO

12)层次化设计 (Hierarchical design )

(三) 芯片时序验证 (PrimeTime)

1)PrimeTime简介 (PT Introduction)

2)PrimeTime数据导入 (Reading Data)

3)静态时序分析基础 (STA Introduction)

4) 时钟约束 (Clock Constraints)

5)时序例外 (Timing Exceptions)

6)时序分析及技巧 (Timing Analysis)

7)物理数据(Physical Data)

8)使用PT ECO 进行快速时 序收敛

9)(PrimeTime ECO) Distributed Multi -Scenario Analysis (DMSA)

10)层次化STA (Hier STA)

(四)芯片功耗与电源分析 (PTPX &Redhawk)

1)芯片功耗分析基础 (Fundamental PowerAnalysis)

2)平均功耗分析 (Average Power Analysis)

3)瞬态功耗分析(Time Based Power Analysis)

4)多电源功耗分析 (MV Power analysis )

5)时钟网络功耗分析 (Clock Network Power Analysis )

6)Redhawk分析流程 (Power analysis flow with Redhawk )

7)电压降和电迁移分析 (IR Drop & EM Analysis)

(五)芯片物理验证 (Calibre)

1)Calibre物理验证流程

2)Calibre DRC分析与修复

3)Calibre LVS分析与修复

九、联系方式

联系人:Gina Hong/021-61154610-8801 张勇021-61154610-8850

邮箱:gina.hong@ssipex.com yong.zhang@ssipex.com

微信:

一、培训对象

1、从事集成电路后端设计实现的初级设计人员(包括应届硕士毕业生);

2、对数字电路布局布线设计感兴趣的微电子行业从业人员。

二、培训目标

1、熟练掌握目前主流的后端布局布线工具ICC;

2、熟练掌握后端布局布线方法;

3、能够使用Calibre,PT,StarRCXT工具;

4、能够独立完成从NETLIST到GDSII的后端布局布线实现过程。

三、培训特色

注重理论和实践的结合,着重实训技能,结合完备的基础理论培训,参照一线公司的验证流程来指导实训为特色。

物理实现方案的制订:包含数据准备,布图布局规划,时钟树综合,布线设计。培训设计人员掌握实际设计流程,培养独立承担复杂布局布线设计的能力。

时序验证和物理验证:包含静态时序分析过程以及物理验证DRC/LVS/ANT/DFM流程和检查方法,让学员掌握严格的验证流程。

四、证书

参加本培训班并通过鉴定者,将由上海市劳动和社会保障局颁发专项职业能力资格证书。

五、 培训费用

1、缴纳上海社保的在职员工收取资料费780元(包括讲义资料费、茶水费等)。

2、无上海社保的学员收取资料费及学费共计2500元。

六、培训计划

1、培训总课时:80课时;

理论培训32课时,采用集中授课、课堂教学结合小组讨论的学习方式;

实训操作培训48课时,采用老师讲解、项目实践、现场指导的学习方式。

2、培训时间:

理论培训4天(每周末一天);

实训操作培训6天(每周末一天)。

3、开班形式:小班授课(40人以下),保证每人1台PC,课上项目实践练习,讲师面授指导和答疑。

七、培训师资

本项目培训师资人员均是具有10年以上专精于集成电路后端布局布线的资深技术人员,拥有对复杂IC后端设计经验、项目管理与带队经验。

vY wang:具有十五年后端布局布线相关工作经验,项目规模在千万门以上,工艺16nm/28nm/40nm。产品涉及手机,无线通信及多媒体终端的核心芯片。

八、课程大纲

(一) 后端布局布线数据的准备

1、理论教学内容

(1)参考库的准备

1)物理库的定义、结构和准备

2)时序库的定义

3)网表库的定义和检查

(2)布图规划

1)电源及物理I/O单元的分类和设计要求

2)芯片布图的方法

3)避免拥塞的方法

4)电源环线和电源条线的规划方法

5)IR DROP分析方法

2、技能实训内容

1)IO单元的摆放

2)MEM/IP的布图规划

3)电源网络的规划和实现

4)IR DROP的检查

(二)布局

1、基础理论教学

(1)扁平化和层次化布局

(2)基于布线拥塞的布局优化

(3)基于时序的布局优化

2、技能实训内容

(1)完成满足时序要求和拥塞要求的扁平化布局

(2)独立完成检查产生的时序报告和拥塞图并可以对应产生优化方案

(三)时钟树综合

1、理论教学内容

(1)时钟信号的定义和结构

(2)建立时钟树的目标和方法

(3)时钟树约束文件及时钟树综合

(4)时钟树综合结果分析和时序分析

2、技能实训内容

(1)能使用ICC工具做时钟树综合

(2)能够使用ICC工具分析时钟树的综合结果

(3)能够通过设置时钟树综合变量来提高时钟树的质量

(四)自动布线设计

1、理论教学内容

(1)全局布线和详细布线的目标和规划

(2)时钟布线和布线修正方法

2、技能实训内容

(1)用ICC工具完成布线流程

(2)掌握NDR RULE在布线中的作用

(3)对布线产生出来的时序问题加以收敛

(4)对布线产生出来的绕线问题进行修正

(五)寄生电阻电容抽取和静态时序分析

1、理论教学内容

(1)StarRCXT工具的使用

(2)SPEF文件介绍

(3)时序分析和优化方法

(4)SDF文件介绍

2、技能实训内容

(1)用StarRCXT工具抽取SPEF文件

(2)用STA工具进行静态时序分析

(3)用STA工具产生修正时序违例的ECO文件,利用ICC工具修复时序问题

(六)形式验证( Formal check)和物理验证(DRC/LVS)

1、理论教学内容

(1)Formal check的原理、设置和比较方法

(2)设计规则检查(DRC)的方法和设置

(3)天线效应及解决方法

(4)LVS纠错方法

(5)DFM定义及提高良率的方法

2、技能实训内容

(1)用Formal工具来完成形式验证,保证网表功能性的正确性

(2)用Calibre工具完成DRC和LVS的物理验证

九、联系方式

联系人:Gina Hong/021-61154610-8801 张勇021-61154610-8850

邮箱:gina.hong@ssipex.com yong.zhang@ssipex.com

微信:

一、培训对象

1、使用FPGA器件进行科研和产品开发的人员;

2、有意从事FPGA设计工作,或者相关领域的人员;

3、从事芯片原型验证的工作人员。

二、培训目标

1、掌握FPGA结构和实现可编程开发的原理;

2、掌握编写Verilog程序的方法,能设计常用数字电路模块,能使用仿真工具验证数字电路设计,能优化数字电路时序设计及功耗设计;

3、熟练使用Vivado工具完成FPGA设计和约束文件的输入、FPGA综合和调试、时序分析和案例分析、FPGA的BIT文件生成、FPGA编程下载及调试;

4、能够生成面向嵌入式软件开发的可编程硬件平台,使用SDK工具运行和调试Zynq异构器件的嵌入式软件,配置和生成bootloader,运行和分析bootloader执行过程, 配置和生成Linux内核和文件系统,运行和分析Linux操作系统执行过程;

5、能够使用Vivado HLS工具对高层次综合输入语言C或C++程序调试,使用Vivado HLS工具设计IP核、分析HLS结果及设计优化,使用SDSoC工具设计可编程异构系统的软硬件程序。

三、培训特色

注重理论和实践的结合, 着重实训技能,结合完备的基础理论培训,参照一线公司的FPGA 的开发流程和设计方法来指导实训为特色。

实现方案的制订:计数器程序的编写,移位寄存器的编写和仿真,FPGA上实现逻辑功能,ZYNQ FPGA上完成SDK平台建立与调试。培训设计人员掌握实际设计流程,培养独立承担FPGA设计工作的能力。

四、证书

缴纳上海社保学员参加本培训班并通过鉴定者,将获得上海市集成电路行业协会颁发,上海市人力资源和社会保障局监制的新技能证书。

五、 培训费用

1、上海市集成电路行业协会会员单位学员收费2000元,鉴定合格退2000元。

2、非上海市集成电路行业协会会员单位学员收费2330元。(费用包括培训费用,以及鉴定费用330元。)

六、培训计划

1、培训总课时:80课时;

理论培训24课时,采用集中授课、课堂教学结合小组讨论的学习方式;

实训操作培训56课时,采用老师讲解、项目实践、现场指导的学习方式。

2、培训时间:

理论培训3天(每周末一天);

实训操作培训7天(每周末一天)。

3、开班形式:小班授课(40人以下),保证每人1台PC,课上项目实践练习,讲师面授指导和答疑。

七、培训师资

本项目培训师资人员均是具有10年以上专精于集成电路设计与验证的资深技术人员,拥有对复杂IC设计验证经验、项目管理与带队经验。

Colin Peng:具有十五年FPGA开发以及设计验证相关工作经验,项目规模在千万门以上。产品涉及交换机、消费类电子、手机等核心芯片。

Deng: 具有十五年FPGA开发以及设计验证相关工作经验,曾在上海贝尔、高通(上海)研发中心等大型世界500强企业工作,担任硬件工程师、研发经理、项目经理、产品总监,从事通讯设备、物联网系统、电梯安全、自动驾驶系统的研发和系统集成。

八、课程大纲

培训单元1. 数字电路设计、仿真与优化

(一)培训主要内容

1.1 理论教学内容

1.1.1 Verilog的基本知识

1.1.2 Verilog数字设计和验证

1.1.3 Verilog的设计规则

1.1.4 数字电路设计方法

1.1.5 数字电路常见模块的理解和设计

1.1.6 仿真工具的使用

1.1.7 仿真验证流程

1.1.8 数字电路速度优化设计技巧

1.1.9 数字电路功耗优化设计技巧

1.2 技能实训内容

1.2.1能编写Verilog程序

1.2.2 能设计常用数字电路模块

1.2.3能使用仿真工具验证数字电路设计

1.2.4能优化数字电路时序设计

1.2.5 能优化数字电路功耗设计

培训单元2 现场可编程门阵列(FPGA)结构和设计优化

(一)培训主要内容

2.1 理论教学内容

2.1.1 FPGA的发展

2.1.2 FPGA结构

2.1.3 逻辑单元

2.1.4 互连结构

2.1.5 IP核资源

2.1.6 高低速接口资源

2.1.7 实验平台介绍

2.1.8 实验操作规范

2.1.9 FPGA设计流程

2.1.10 常用IP核的使用

2.1.11 综合和约束

2.1.12 时序分析

2.1.13 实现和编程

2.1.14 内部逻辑调试

2.1.15 设计优化

2.2 技能实训内容

2.2.1 能使用Vivado工具完成FPGA设计和约束文件的输入

2.2.2 能使用Vivado工具完成FPGA综合和调试

2.2.3 能使用Vivado工具完成时序分析和案例分析

2.2.4 能使用Vivado工具完成FPGA位流生成和编程下载

2.2.5 能使用Vivado工具完成FPGA内部逻辑调试和设计修改

培训单元3 可编程异构系统的嵌入式软件设计

(一)培训主要内容

3.1 理论教学内容

3.1.1 Zynq异构器件架构

3.1.2 Zynq器件开发流程

3.1.3 Zynq嵌入式软件开发流程

3.1.4 掌握嵌入式软件的运行和调试

3.1.5 能理解Bootloader执行过程

3.1.6 能掌握Bootloader调试

3.1.7 能理解嵌入式Linux的执行流程

3.1.8能掌握嵌入式Linux的调试

3.2 技能实训内容

3.2.1能生成面向嵌入式软件开发的可编程硬件平台

3.2.2 能使用SDK工具运行和调试Zynq异构器件的嵌入式软入

3.2.3配置和生成bootloader

3.2.4 运行和分析bootloader执行过程

3.2.5 配置和生成Linux内核和文件系统

3.2.6 运行和分析Linux操作系统执行过程

培训单元4 高层综合原理和设计优化

(一)培训主要内容

4.1 理论教学内容

4.1.1 高层综合原理和流程

4.1.2 Vivado HLS设计流程

4.1.3 Vivado HLS设计实例

4.1.4 Vivado HLS设计分析

4.1.5 可编程异构系统的软硬件设计流程

4.1.6 分析和优化软硬件设计

4.1.7 评估软硬件设计性能

4.2 技能实训内容

4.2.1 能使用Vivado HLS工具对高层次综合输入语言C或C++程序调试

4.2.2 能使用Vivado HLS工具设计IP核

4.2.3 能分析HLS结果,设计优化

4.2.4 能使用SDSoC工具设计可编程异构系统的软硬件程序

九、联系方式

联系人:Gina Hong/021-61154610-8801 张勇021-61154610-8850

邮箱:gina.hong@ssipex.com yong.zhang@ssipex.com

微信:

一、培训对象

1、从事集成电路设计、制造等相关行业的人员;

2、从事集成电路封装、测试等相关行业的人员;

3、从事PCB设计、PCB制造、智能卡、设备材料及系统设计等相关行业的人员。

二、培训目标

1、掌握芯片接口电路的基本知识,能利用Hspice工具完成常见的电路仿真;

2、掌握芯片接口电路模型的IBIS建模方法,能利用T2B、XtractIM工具完成芯片IBIS建模和封装参数提取工作;

3、掌握芯片接口电路IBIS模型的测试验证和应用,掌握信号完整性基础知识。

三、培训特色

注重理论和实践的结合,着重实训技能,结合完备的基础理论培训,参照一线公司的验证流程来指导实训为特色;

理论知识讲解详细,既有基本的规范解释、电路结构分析,也有业界目前最流行的建模方法、EDA工具介绍以及应用场景介绍;

实践操作案例充分,与教材紧密结合,与公司的实际需求贴近,让参会人员能够在本次培训课上完之后胜任各种常见的接口电路建模工作。

四、培训费用

培训费2500元。包含教材费、场地费、线上平台、实训账号等。

五、培训计划

1、线下培训总课时:80个课时(线下课程为主,线上课程为辅),持续2-3个月(课时按实际课程进度进行调整)

2、培训时间:每周末一天(国家法定假日另行安排)

3、培训地点:上海硅知识产权交易中心(宜山路333号汇鑫国际大厦1号楼1706室)

4、开班形式:小班授课,保证每人1台PC;全流程开通vnc登录账号,任何时间随时登录进行工具学习和实战操作,授课老师提供技术支持与答疑

5、开班时间:招满即开

六、培训师资

本项目培训师资人员均是具有10年以上专精于 集成电路、封装和PCB仿真测试方面的资深专家,拥有 丰富的芯片及系统仿真 经验、项目管理与带队经验。

l Jason Hu

具有十四年芯片接口电路建模与SI/PI/EMI系统仿真经验,精通芯片、封装和PCB等各个层级的建模。曾参与多款主流服务器、笔记本、数字家庭和手机系统的研发工作,负责过其中电脑CPU、通信芯片和手机芯片的高速接口建模及仿真工作,涉及到的高速接口包括:DDR2/3/4、LPDDR2/3/4、PCIe Gen2/3、USB2/3、MIPI和HDMI等。同时培训经验丰富,曾为国内外20多家知名公司提供过建模和仿真方面的技术支持和培训。

七、课程大纲

培训单元1 芯片接口电路模型及SPICE介绍

(一)培训主要内容

1.1 理论教学内容

1.1.1 芯片接口电路模型种类

1.1.2 SPICE描述语言发展简介

1.1.3 SPICE语言的基本词法介绍

1.1.4 SPICE电路的基本单位介绍

1.1.5 SPICE电路的器件定义介绍

1.1.6 SPICE电路的激励源介绍

1.1.7 SPICE电路的器件模型介绍

1.1.8 SPICE电路的分析类型语句介绍

1.1.9 SPICE电路的控制语句和Option语句介绍

1.1.10 SPICE电路的输出格式描述语句介绍

1.1.11 SPICE电路的特性分析语句介绍

1.1.12 SPICE电路的特性控制语句介绍

1.1.13 总结与进阶

1.2 技能实训内容

1.2.1 无源器件模型的SPICE编程

1.2.2 S参数模型的调用SPICE编程

1.2.3 理想传输线使用的SPICE编程

1.2.4 子电路SPICE编程

1.2.5 IBIS模型调用spice编程

培训单元2 芯片接口电路模型IBIS的建模

(一)培训主要内容

2.1 理论教学内容

2.1.1 IBIS模型简介

2.1.2 芯片接口电路建模流程与方法

2.1.3 IBIS模型类型介绍

2.1.4 I/O电路结构

2.1.5 常见I/O逻辑电路

2.1.6 高速并行接口

2.1.7 高速串行接口

2.1.8 IBIS波形曲线

2.1.9 IBIS文件通用属性

2.1.10 芯片封装结构的种类

2.1.11 芯片封装寄生参数RLC

2.1.12 IBIS文件的头文件与结束

2.1.13 IBIS文件的Pin 引脚RLC

2.1.14 IBIS文件的Diff Pin与驱动能力选择

2.1.15 IBIS文件通用规则介绍

2.1.16 T2B IBIS建模演示

2.2 技能实训内容

2.2.1 单端Input电路的IBIS模型提取

2.2.2 单端Output电路的IBIS模型提取

2.2.3 单端I/O电路的IBIS模型提取

2.2.4 芯片封装模型的参数提取

2.2.5 伪差分I/O电路的IBIS模型提取

2.2.6 真差分LVDS输出电路的IBIS模型提取

培训单元3 芯片接口电路IBIS的测试验证与信号完整性基础

(一)培训主要内容

3.1 理论教学内容

3.1.1 芯片接口电路仿真测试的流程与方法

3.1.2 通信系统知识介绍

3.1.3 信号的种类介绍

3.1.4 信号运算介绍

3.1.5 信号质量标准介绍

3.1.6 信号完整性概念

3.1.7 On-die电源网络介绍

3.1.8 电源系统建模介绍

3.1.9 电源系统分析

3.1.10 Cadence SI/PI仿真工具简介

3.2 技能实训内容

3.2.1 对单端Input电路进行IBIS和Spice验证分析

3.2.2 对单端Output电路进行IBIS和Spice验证分析

3.2.3 对单端I/O电路进行IBIS和Spice验证分析

3.2.4 对伪差分I/O电路进行IBIS和Spice验证分析

3.2.5 对真差分LVDS输出电路进行IBIS和Spice验证分析

八、联系方式

联系人:Gina Hong/021-61154610-8801 张勇021-61154610-8850

邮箱:gina.hong@ssipex.com yong.zhang@ssipex.com

微信:

一、培训对象

1、从事集成电路设计的工作的人员。

2、有意从事集成电路DFT设计和验证的工作人员。

二、培训目标

1、了解集成电路测试的基本概念,可测性设计的基本原理,熟悉目前工业界主流的可测试设计方法。

2、掌握边界扫描链(Boundary Scan)技术, 能够独立设计所需硬件逻辑。

3、掌握扫描链(scan)插入技术,理解常见的stuck at , transiton, path delay, IDDQ等故障测试。

4. 理解片上时钟控制(OCC)对于at speed测试的意义,理解并掌握scan compression技术。

5、掌握ATPG实现技术,能够基于Mentor Flow进行测试向量生成并验证。

6、掌握Mbist实现技术,能够基于Mentor Flow进行Mbist逻辑插入以及验证。

7、能够结合所学测试方法学、进行SOC芯片的可测性结构设计,制定测试方案,实现测试结构,验证测试结果,覆盖率收集,以及成品率的估算。

8、理解 mbist诊断和scan诊断对于芯片制造良率提升的重要意义,掌握基本的测试诊断流程。

9、能够参考业界一流公司的可测试设计验证流程,能完成相关的文档并逐一答辩通过。

三、培训特色

?注重理论和实践的结合,着重实训技能,结合完备的基础理论培训,参照一线公司的可测试设计验证流程来指导实训为特色

1、可测试方法学:涵盖复杂SOC里不同模块的可测试方法实现,包含针对PAD测试的边界扫描测试,针对数字逻辑的扫描链测试,针对存储器的自测试方法。

2、可测试方案的制订:包括测试目标要求制定,测试方法和平台的选择,测试激励的生成和验证,覆盖率保证,成品率分析,测试成本估算以及开发进度的保证等等。需要可测试开发人员准备相关的文档进行答辩,来培养独立承担复杂芯片测试的能力。

3、可测试覆盖率的收敛:包含可测试覆盖率的收集,提高可测试覆盖率的方法,以及可测试覆盖率对最后产品良率的影响。让学员按照严格的流程来通过可测试结果验收。

四、 培训费用

培训费2500元。包含教材费、场地费、线上平台、实训账号等。

五、培训计划

1、线下培训总课时:80个课时(线下课程为主,线上课程为辅),持续2-3个月(课时按实际课程进度进行调整)

2、培训时间:每周末一天(国家法定假日另行安排)

3、培训地点:上海硅知识产权交易中心(宜山路333号汇鑫国际大厦1号楼1706室)

4、开班形式:小班授课,保证每人1台PC;全流程开通vnc登录账号,任何时间随时登录进行工具学习和实战操作,授课老师提供技术支持与答疑

5、开班时间:招满即开

六、培训师资

本项目培训师资人员均是具有10年以上专精于集成电路验证的资深专家,拥有对复杂SoC的可测试设计验证经验、项目管理与带队经验。

七、课程大纲

(一)芯片可测试性电路设计仿真基础

1、理论教学内容

(1)芯片测试的基本概念

(2)芯片测试流程

(3)自动测试设备介绍

(4)可测试设计基本概念

(5)常用可测试设计方法

(6)故障建模和常见模型

(二)边界扫描法

1、理论教学内容

(1)JTAG(IEEE1149.1)基本原理

(2)边界扫描法基本结构和指令

(3)边界扫描测试流程

(4)边界扫描描述语言

(5)JTAG和边界扫描的验证

2、技能实训内容

(1)使用Verilog编写Tap控制器

(2)使用Verilog添加BS-1149.1寄存器

(3)实现边界扫描的功能测试

(三)扫描链测试法

1、理论教学内容

(1)扫描链设计的基本原理

1)扫描链电路的结构和原理

2)ATPG(自动激励生成)的原理

3)ATPG故障类型介绍

4)扫描链电路设计基本流程

(2)扫描链插入的基本流程(基于Tessent Scan)

1)扫描链插入相关逻辑功能

2)扫描链插入的准备

3)扫描链插入基本命令和功能

4)扫描链插入结果检查

(3)ATPG(自动激励生成)的基本流程(基于TessentFastScan)

1)ATPG实现的准备

2)ATPG实现的基本命令和功能

3)ATPG 设计规则检查

4)ATPG覆盖率收集和分析

(4)扫描链电路验证基本流程

1)验证的分类和原理

2)验证文件的准备

3)验证实现方法

4)验证结果检查

5)验证调试方法

2、技能实训内容

(1)实现电路的扫描链插入

(2)实现电路的自动激励生成(ATPG)

(3)实现电路的扫描链验证

(四)内建自测试

1、理论教学内容

(1)内建自测试设计的基本原理

1)存储器单元功能和原理

2)存储器故障原理

3)内建自测试方法

4)内建自测试电路结构和设计原理

(2)内建自测试设计流程(基于TessentMbist)

1)内建自测试的设计规则检查

2)内建自测试的设计规划

3)内建自测试的设计实现

(3)内建自测试验证流程

1)内建自测试的验证

2、技能实训内容

(1)实现电路的内建自测试设计

(2)实现电路的内建自测试验证

八、联系方式

联系人:Gina Hong/021-61154610-8801 张勇021-61154610-8850

邮箱:gina.hong@ssipex.com yong.zhang@ssipex.com

微信:

一、培训对象

1、从事模拟集成电路设计的工作的人员;

2、有意从事模拟集成电路设计的工作的人员。

二、培训目标

1、熟练掌握运算放大器原理,掌握稳定性和频率补偿的方法;

2、能够制作和使用跨导效率查找表;

3、能够应用Matlab来系统优化设计运算放大器电路;

4、能够用Cadence电路设计工具设计运算放大器的原理图和符号;

5、能够用Cadence ADE仿真环境和Spectre仿真器进行运算放大器仿真;

6、能够分析运算放大器的仿真结果。

三、培训特色

?注重理论和实践的结合,着重实训技能结合完备的基础理论培训,参照国际先进的运算放大器设计方法来指导实训为特色。

1、系统地介绍运算放大器电路原理,电子电路的频率相信分析方法,反馈放大器原理,放大器稳定性和频率补偿方法,运算放大器的性能参数。先进的利用跨导效率来系统地设计运算放大器的方法,运用Matlab和Spectre来产生SPICE跨导效率查找表,通过查找表来确定MOS晶体管的尺寸。用跨导效率作为模拟电路设计折衷的中心变量,一些基于Matlab程序脚本的设计流程,可以方便快速准确地设计运算放大器各个MOS晶体管的尺寸。

2、利用Cadence IC设计工具建立运算放大器原理图和电路符号,再运用Cadence ADE和Spectre对运算放大器的性能进行仿真。理论与实践操作相结合。

四、证书

参加本培训班并通过鉴定者,将由上海市劳动和社会保障局颁发专项职业能力资格证书。

五、 培训费用

1、缴纳上海社保的在职员工收取资料费780元(包括讲义资料费、茶水费等)

2、无上海社保的学员收取资料费及学费共计2500元

六、培训计划

1、培训总课时:80课时。

理论培训:36课时,采用课堂教学培训方式结合小组讨论的理论知识培训方法。;

操作技能:44课时,采用教师讲解结合项目实践、现场指导和在线练习的学习方式。

2、培训时间:每周日,共10天(除国家法定假日)

4、培训地点:上海硅知识产权交易中心(宜山路333号汇鑫国际大厦1号楼1706室)

5、开班形式:小班授课(40人以下),保证每人1台PC;同时开通云端服务器登录账号,可随时登录进行项目实训,授课老师提供技术支持与答疑。

七、培训师资

本项目培训师资人员均是具有10年以上专精于模拟集成电路设计的资深专家,拥有丰富的CMOS模拟集成电路设计仿真经验、项目管理与带队经验。

lPaul Fu

拥有十五年的CMOS模拟集成电路设计经验。对运算放大器,LDO,Charge pump,Bandgap,ADC,MCU等有丰富的理论和实践经验。尤其在运算放大器方向,精通各种运算放大器方面,涵盖几乎所有领域:低失调运放,高速运算放大器,高压高功率运放,Class-D功率放大器等。同时拥有MCU领域的团队技术管理和带团队经验。

八、课程大纲

(一)运算放大器电路原理

1、理论教学内容

(1)MOS晶体管工作原理

(2)单级放大器原理

(3)电子电路的频率响应分析方法

(4)反馈放大器原理

(5)运算放大器性能参数

(6)折叠共源共栅运算放大器原理

(7)两级运算放大器原理

(8)稳定性和频率补偿的方法

(9)Spectre器件描述方法

(10)Spectre电路仿真

(11)跨导效率的设计方法

(12)制作跨导效率查找表的方法

(13)用跨导效率设计放大器的方法

2、技能实训内容

(1)反馈电路中的放大器计算

(2)两级运算放大器补偿电容计算

(3)共源放大器增益带宽仿真

(4)跨导效率查找表的制作

(5)跨导效率查找表的使用

(二)运算放大器电路设计

1、基础理论教学

(1)Matlab矩阵操作

(2)Matlab文件操作

(3)Matlab编程

(4)开关电容电路中的运算跨导放大器系统优化设计实现方法

(5)折叠共源共栅运算放大器系统优化设计实现方法

(6)两级运算放大器系统优化设计实现方法

(7)运算放大器的版图设计考虑

(8)Cadence IC工具建立运算放大器电路原理图和电路符号

2、技能实训内容

(1)Matlab编程

(2)系统优化设计折叠共源共栅运算放大器电路参数

(3)系统优化设计两级运算放大器电路参数

(4)绘制折叠共源共栅运算放大器原理图

(5)绘制运算放大器电路符号

(三)运算放大器电路仿真

1、理论教学内容

(1)Cadence ADE的环境设置方法

(2)Spectre直流分析仿真

(3)Spectre瞬态分析仿真

(4)Spectre交流分析仿真

(5)Spectre零极点仿真

(6)运算放大器性能仿真

(7)蒙特卡罗仿真

(8)多工艺角仿真

(9)波形显示窗口

(10)结果浏览器

(11)计算器工具

2、技能实训内容

(1)Cadence ADE的环境设置

(2)运算放大器交流分析仿真

(3)运算放大器压摆率仿真能力

(4)运算放大器电源抑制比仿真能力

(5)运算放大器共模抑制比仿真能力

九、联系方式

联系人:Gina Hong/021-61154610-8801 张勇021-61154610-8850

邮箱:gina.hong@ssipex.com yong.zhang@ssipex.com

微信: